Synchronized Debugging for AURIX Multi-Chip Systems

Lauta (Germany), October 4, 2018 – With the new Multi-Target Debug Adapter suitable for the Universal Access Device 3+ (UAD3+) of the UDE® Universal Debug Engine, PLS Programmierbare Logik & Systeme presents the first tool that allows synchronous debugging of multi-chip systems.

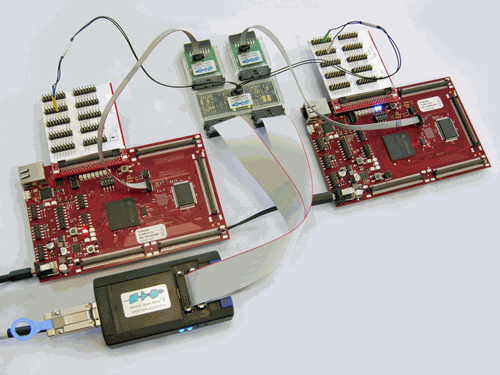

PLS’s modular Multi-Target Debug Adapters support various high-performance systems with two separate microcontrollers on one board, which enable redundant and, where appropriate, inverted control algorithms. A particular special focus is placed on future applications with highest demands on functional safety and fault tolerance, for example, fail-operational systems in the field of autonomous driving. But also for current high-performance automotive systems, the toolkit proves its unique debug capabilities, for example, for the recently released Automotive Gateway Evaluation Board from Infineon with two AURIX™ multicore microcontrollers.

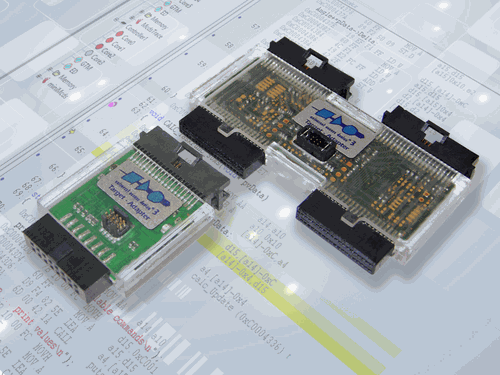

The Multi-Target Debug Adapter for the UAD3+ enables almost synchronous stopping and restarting of two tightly coupled AURIX™ microcontrollers. A standard debug adapter is connected to each of the separate debug interfaces of the two AURIX™ devices. These are then connected via the Multi-Target Debug Adapter to a debug pod of the UAD3+, which provides the two necessary debug channels.

In addition to connectors for the standard debug adapters, the Multi-Target Debug Adapter has an additional connector for particular trigger signals of the two AURIX™ controllers. The special logic of the Multi-Target Debug Adapter links the trigger lines in such a way that the two AURIX™ microcontrollers can be stopped and restarted almost synchronously. It does not matter whether the entire system reacts to a breakpoint in one of the two controllers or to a break action triggered by the user. The time difference, caused by the internal logic of the adapter and the signal propagation delays between the two controllers, is on average only about 65 ns when stopping or restarting. That is less than 20 clock cycles at a typical 300 MHz clock frequency.

Both AURIX™ microcontrollers are accessible and controllable in one debug session within a common, consistent user interface. Of course, the established multicore run control management of the UDE® is also available for debugging of multiple AURIX™ platforms. In a run control group all cores or a definable number of cores of the two controllers can be combined, so breakpoints, manual stopping and synchronous restarting become effective for all cores of that group.