Hardware Appendix to the Software Guide to

# UDE<sup>®</sup> Universal Debug Engine Debugging, Trace and Test for Embedded Systems

Integrated Development Environment for 64-, 32-, 16-bit Microcontrollers and Embedded Processors

AURIX, TriCore, Arm Cortex-M/R/A, Arm7/9/11, S32G/S/V, Stellar G/P/E, RH850, R-Car, RISC-V, ARC, Power Architecture

© **PLS** 1991-2025 V 2025.1.2

This manual contains 167 pages.

#### Contact us at:

E-Mail: <u>support@pls-mc.com</u> <u>info@pls-mc.com</u> WWW: https://www.pls-mc.com/

| PLS Programmierbare Logik & Systeme GmbH |                    | PLS Development Tools             |                 |  |

|------------------------------------------|--------------------|-----------------------------------|-----------------|--|

| Technologiepa                            | ark Lauta          | 10080 N. Wolfe Rd., Suite SW3-200 |                 |  |

| DE-02991 Lau                             | ita                | Cupertino, CA                     | 95014           |  |

| Germany                                  |                    | USA                               |                 |  |

| Phone:                                   | + 49 35722 384 - 0 | Phone:                            | +1-949-863-0327 |  |

|                                          |                    | Toll Free:                        | +1-877-77-DEBUG |  |

All rights reserved. No part of this manual may be reproduced or may be transmitted in any form or by any means without prior written permission of PLS Programmierbare Logik & Systeme GmbH (PLS). The information in this manual is subject to change without notice, no responsibility is assumed for its use. **UDE<sup>®</sup> Universal Debug Engine** is a trademark of PLS Programmierbare Logik & Systeme GmbH. Adobe® is a registered trademark of Adobe Systems Incorporated. AURIX<sup>™</sup>, TriCore<sup>™</sup> are trademarks of Infineon AG. ARM7<sup>™</sup>, ARM9<sup>™</sup>, ARM11<sup>™</sup>, Cortex<sup>™</sup> are trademarks of ARM®. PowerPC® is a registered trademark of IBM Corporation, Power Architecture<sup>™</sup> is a trademark of IBM Corporation. RISC-V® is a registered trademark of RISC-V International. ARC® is a registered trademark of Synopsys<sup>®</sup>. Windows®10, Windows®11 are trademarks of Microsoft Corporation. Pentium® and Core<sup>™</sup> are trademarks of Intel Corporation. XScale<sup>®</sup>, Celeron<sup>®</sup> are registered trademarks of Intel Corporation. Athlon<sup>™</sup> is a trademark of Renesas Technology Corporation. All other names and trademarks are the property of their respective owners.

PLS reserves the right to make technical changes to the equipment or changes to this document without any prior notice.

# Contents

| Introduction                                                                                                                                                                                                                                                                               |                                                     | 7                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|

| Overview<br>Feedback                                                                                                                                                                                                                                                                       |                                                     | 7<br>7                                                               |

| Appendix A – Safety Instruction                                                                                                                                                                                                                                                            | ons                                                 | 9                                                                    |

| Safety Instructions for Product<br>Regulatory Complianc<br>Software<br>Electrical Safety Instru<br>Mechanical Safety Ins<br>Safety Instructions<br>Static Electricity Precautions<br>Firmware updates<br>Original Components of Delive                                                     | e and Compliance Statements<br>actions<br>tructions | 9<br>10<br>10<br>10<br>11<br>12<br>13<br>14<br>14                    |

| Appendix A.1 – Hardware Des                                                                                                                                                                                                                                                                | cription UAD2 <sup>*)</sup>                         | 15                                                                   |

| Description<br>Product Features<br>Precautions of Firmware updat<br>Power Supply<br>Driver Installation USB<br>Interface and Connector Descr<br>Overview<br>Access Device Status<br>Interface Details<br>Resetting the Target Systems<br>Static Electricity Precautions                    | ription                                             | 15<br>16<br>16<br>16<br>16<br>17<br>17<br>17<br>18<br>25<br>26       |

| Appendix A.2 – Hardware Des                                                                                                                                                                                                                                                                | cription UAD2 <sup>pro</sup>                        | 27                                                                   |

| Description<br>Product Features<br>Precautions of Firmware updat<br>Power Supply<br>Driver Installation USB<br>Interface and Connector Descr<br>Overview<br>Access Device State In<br>Debug Adapter<br>Interface Details<br>Resetting the Target Systems<br>Static Electricity Precautions | ription                                             | 27<br>28<br>28<br>28<br>28<br>29<br>29<br>29<br>30<br>31<br>40<br>41 |

| Appendix A.3 – Hardware Des                                                                                                                                                                                                                                                                | cription UAD2+ *)                                   | 42                                                                   |

| Description<br>Product Features<br>Precautions of Firmware updat<br>Power Supply<br>Driver Installation IEEE1394<br>Driver Installation USB                                                                                                                                                | tes                                                 | 42<br>42<br>43<br>43<br>43<br>43                                     |

| Driver Installation Ethernet TCP/IP                                             | 44         |

|---------------------------------------------------------------------------------|------------|

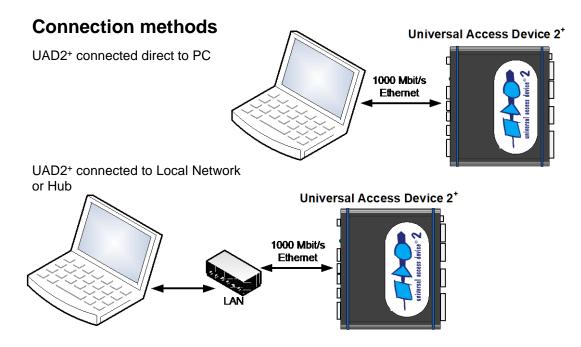

| Connection methods                                                              | 44         |

| DHCP or static IP addressing                                                    | 44         |

| Determining the MAC address                                                     | 46         |

| Application hints                                                               | 46         |

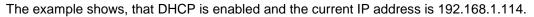

| Interface and Connector Description                                             | 47         |

| Overview                                                                        | 47         |

| Access Device Status Indication                                                 | 48         |

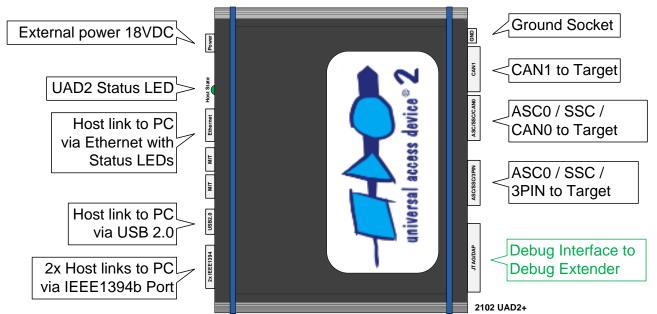

| Debug Adapter                                                                   | 48         |

| Interface Details                                                               | 49         |

| Resetting the Target Systems                                                    | 62<br>63   |

| Static Electricity Precautions                                                  |            |

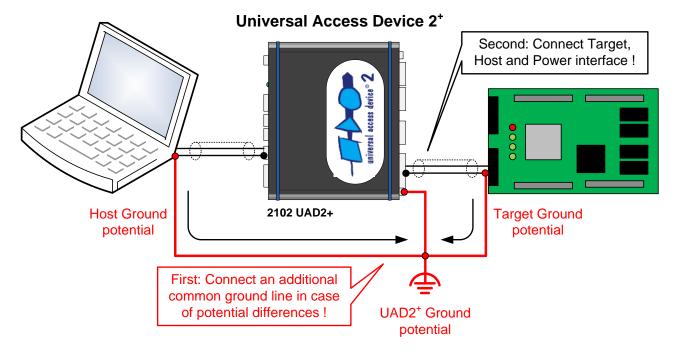

| Appendix A.4 – Hardware Description UAD2 <sup>+</sup> Trace Board <sup>*)</sup> | 64         |

| Description                                                                     | 64         |

| Product Features                                                                | 64         |

| Trace Pod Calibration<br>Technical details                                      | 65         |

|                                                                                 | 66<br>67   |

| Trace Pod Setup                                                                 | 67         |

| Interface and Connector Description<br>Overview                                 | 68<br>68   |

| Interface Details                                                               | 69         |

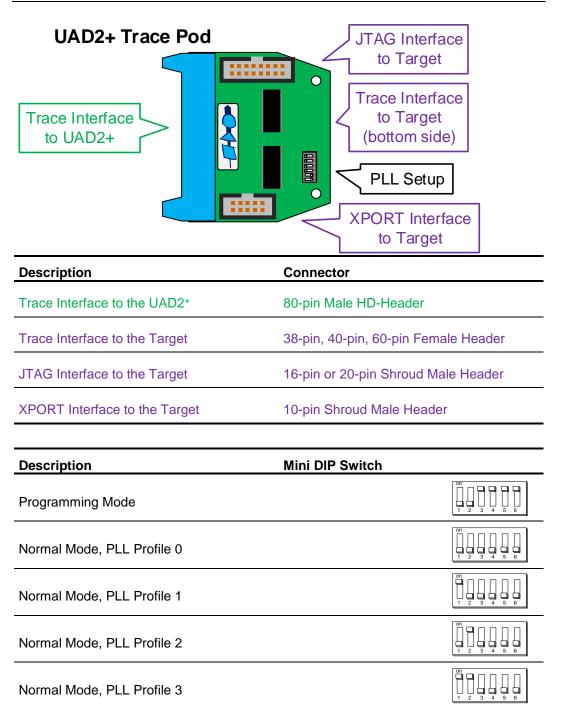

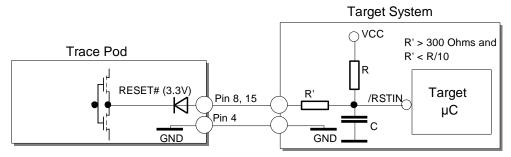

| Resetting the Target Systems                                                    | 75         |

| Static Electricity Precautions                                                  | 76         |

| Appendix A.5 – Hardware Description UAD2 <sup>next</sup>                        | 77         |

| Description                                                                     | 77         |

| Product Features                                                                | 77         |

| Precautions of Firmware updates                                                 | 78         |

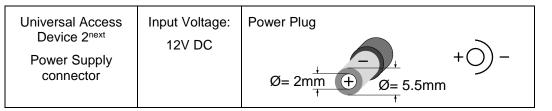

| Power Supply                                                                    | 78         |

| Driver Installation USB                                                         | 78         |

| Driver Installation Ethernet TCP/IP                                             | 79         |

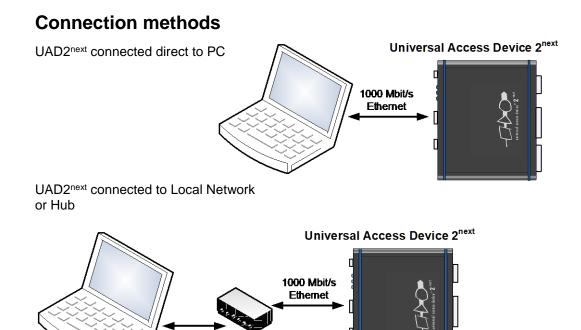

| Connection methods                                                              | 79         |

| DHCP or static IP addressing                                                    | 79         |

| Determining the MAC address                                                     | 81         |

| Application hints                                                               | 81         |

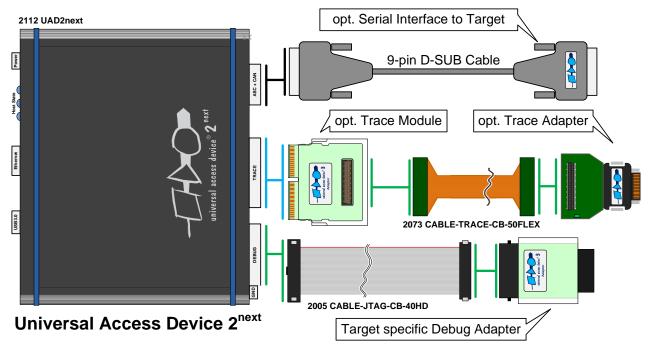

| Interface and Connector Description                                             | 82         |

| Overview                                                                        | 82         |

| Access Device State Indication                                                  | 82         |

| Debug Adapter                                                                   | 83         |

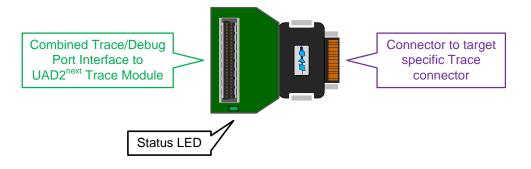

| UAD2 <sup>next</sup> Trace Modules                                              | 84         |

| Interface Details                                                               | 88         |

| Resetting the Target Systems<br>Static Electricity Precautions                  | 103<br>104 |

| Appendix A.6 – Hardware Description UAD3 <sup>+</sup>                           | 105        |

| Description                                                                     | 105        |

| Product Features                                                                | 105        |

| Precautions of Firmware updates                                                 | 106        |

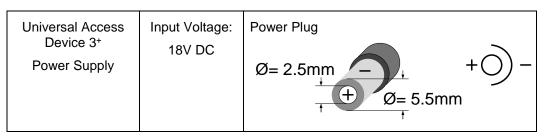

| Power Supply                                                                    | 106        |

| Driver Installation IEEE1394b                                                   | 107        |

| Driver Installation USB                                                         | 107        |

| Driver Installation Ethernet TCP/IP                                             | 107        |

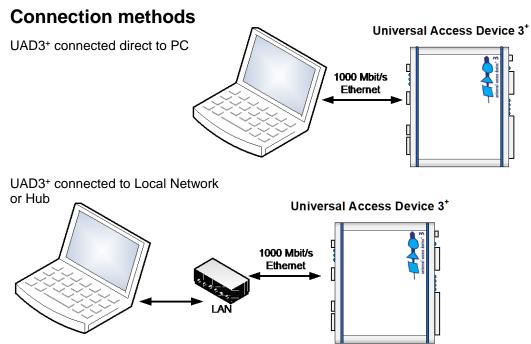

| Connection methods                                                              | 107        |

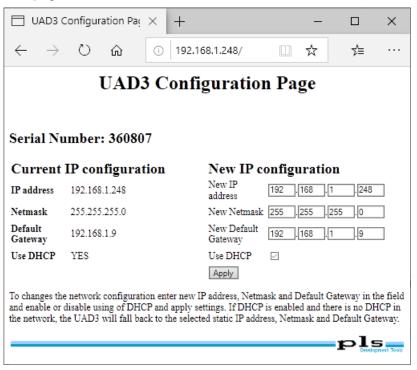

| DHCP or static IP addressing                                                    | 107        |

| Determining the MAC address                                                     | 109        |

| Application hints                                                               | 109        |

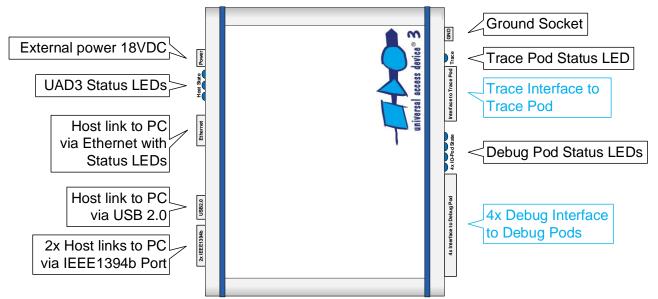

| Interface and Connector Description                                             | 110        |

| Overview                                                                        | 110        |

| Access Device Status Indication                                                 | 111        |

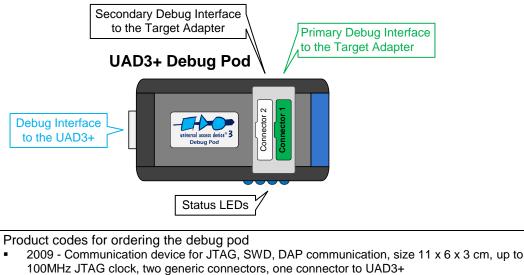

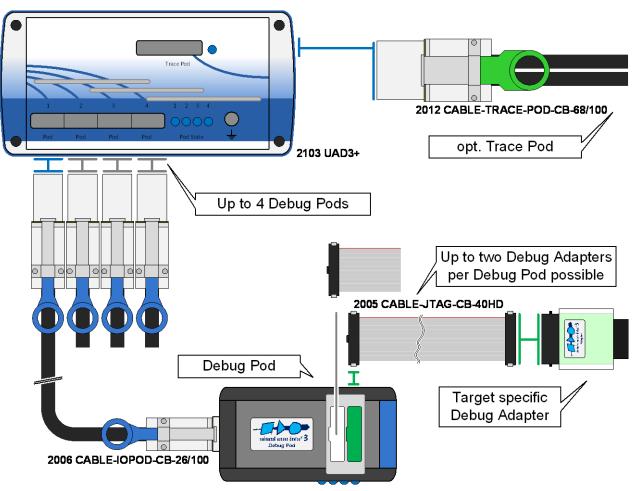

| UAD3 <sup>+</sup> Debug Pod                                                     | 112        |

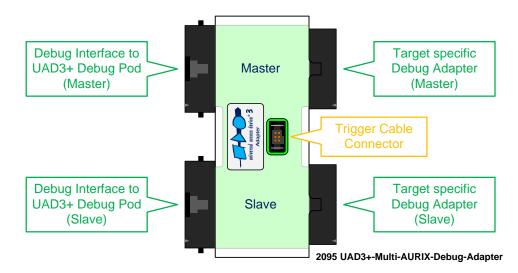

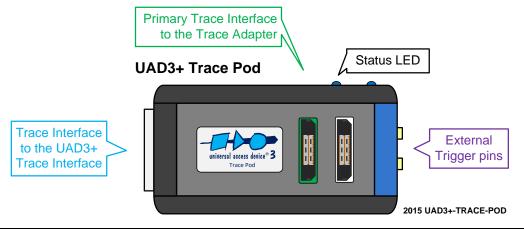

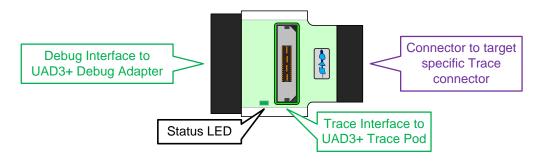

| Debug Adapter<br>UAD3+ Multi AURIX Adapter<br>UAD3+ Trace Pod                                                                      | 114<br>115<br>116 |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------|

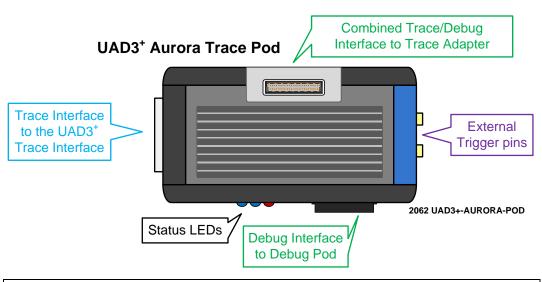

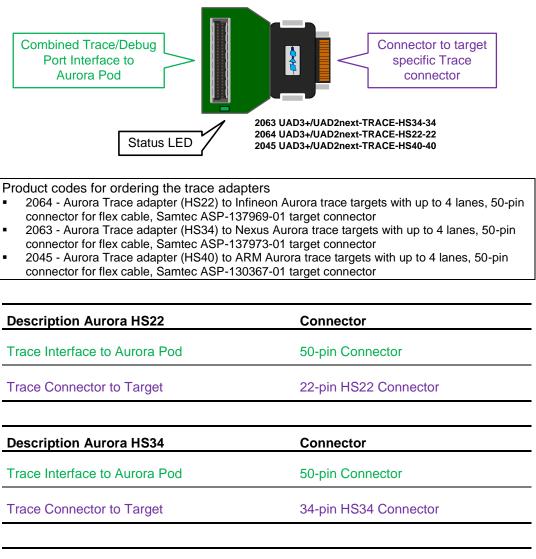

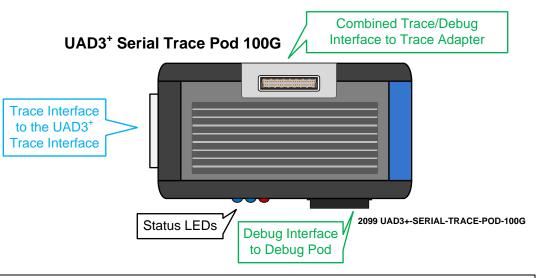

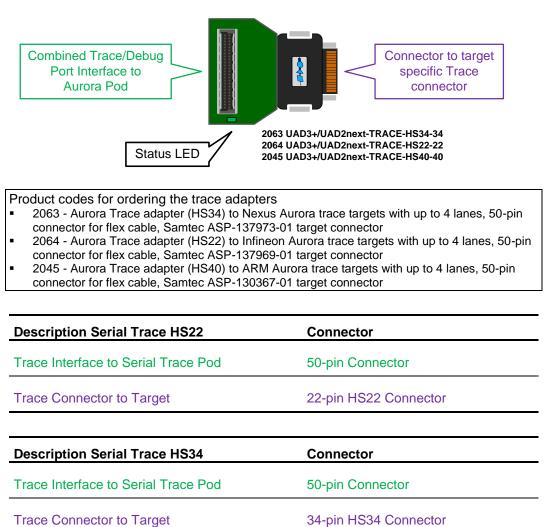

| UAD3 <sup>+</sup> Aurora Trace Pod<br>UAD3 <sup>+</sup> Serial Trace Pod 100G<br>Interface Details                                 | 118<br>120<br>122 |

| Resetting the Target Systems<br>Debug/Trace Pod Configuration for UAD3 <sup>+</sup><br>UDE <sup>®</sup> Access Device Configurator | 137<br>137<br>137 |

| Static Electricity Precautions                                                                                                     | 140               |

| Appendix A.7 – Hardware Description JTAG-Protector 2                                                                               | 141               |

| Description<br>Product Features                                                                                                    | 141<br>141        |

| Electrical properties                                                                                                              | 141               |

| Installation                                                                                                                       | 142<br>142        |

| Interface and Connector Description<br>Interface Details                                                                           | 142               |

| Appendix B – Compatibility List                                                                                                    | 143               |

| UDE <sup>®</sup> Universal Debug Engine<br>Microcontrollers                                                                        | 143<br>144        |

| 32-Bit TriCore™ Derivatives (Infineon Technologies)                                                                                | 144               |

| 32-Bit Traveo™ Derivatives (Infineon Technologies)                                                                                 | 144               |

| 32-Bit MOTIX™ Derivatives (Infineon Technologies)<br>32-Bit PowerPC® and PowerArchitecture™ Derivatives                            | 144<br>144        |

| 64-Bit Cortex-A53™ Derivatives                                                                                                     | 144               |

| 32-Bit Cortex-R52™ Derivatives                                                                                                     | 145               |

| 32-Bit RISC-V™ Derivatives<br>32-Bit Cortex-M0, -M3, -M33, -M4, -M7, -R4, -R5F, -R52, -A8, -A9™                                    | 145               |

| Derivatives                                                                                                                        | 145               |

| 32-Bit ARM7™, ARM9™, ARM11™, XScale Derivatives                                                                                    | 145<br>145        |

| 32-Bit SuperH™ SH-2A Derivatives<br>32-Bit RH850 Derivatives                                                                       | 145               |

| 32-Bit Synopsys ARC <sup>®</sup> Derivatives                                                                                       | 146               |

| 16-Bit C166 Derivatives (Infineon Technologies)                                                                                    | 146               |

| 16-Bit C166 Derivatives* (Micronas Semiconductor)<br>16-Bit ST10 Derivatives* (STMicroelectronics)                                 | 146<br>146        |

| Simulators                                                                                                                         | 146               |

| 32-Bit Power Architecture™ Derivatives                                                                                             | 146               |

| 32-Bit TriCore™ Derivatives (Infineon Technologies)<br>Compilers                                                                   | 146<br>147        |

| Supported output formats of binary and debug information                                                                           | 147               |

| TriCore™ Compiler                                                                                                                  | 147               |

| Power Architecture® Compiler<br>Cortex-M/R/A, ARM7™, ARM9™, ARM11™, XScale Compiler                                                | 147<br>147        |

| SuperH SH-2A Compiler                                                                                                              | 147               |

| C166*, ST10*, XC166, XC2000 Compiler                                                                                               | 147               |

| Real Time Operating Systems<br>Other Software Tools                                                                                | 148<br>148        |

| Other Hardware tools                                                                                                               | 148               |

| Supported USB-to-Serial converter                                                                                                  | 148               |

| Appendix C – Trouble Shooting                                                                                                      | 149               |

| Trouble Shooting Checklist<br>Latest Versions on World Wide Web                                                                    | 149<br>149        |

| Known Issues with UDE®                                                                                                             | 149               |

| How to report errors                                                                                                               | 150               |

| Appendix D - CE Declarations                                                                                                       | 151               |

## Appendix E - Copyrights

| ndix E - Copyrights                                                     | 159             |

|-------------------------------------------------------------------------|-----------------|

| List of Open Source Software Components                                 | 159             |

| IwIP Software License: Adam Dunkels                                     | 159             |

| IwIP Software License: Axon Digital Design                              | 159             |

| IwIP Software License: Carnegie Mellon University                       | 159             |

| IwIP Software License: Christophe Devine                                | 159             |

| IwIP Software License: CITEL Technologies Ltd                           | 160             |

| IwIP Software License: Cognizant Pty Ltd                                | 160             |

| IwIP Software License: Dominik Spies                                    | 160             |

| IwIP Software License: Eric Rosenquist                                  | 160             |

| IwIP Software License: Global Election Systems Inc                      | 160             |

| IwIP Software License: Google Inc                                       | 160             |

| IwIP Software License: Inico Technologies Ltd                           | 161             |

| IwIP Software License: Leon Woestenberg                                 | 161             |

| IwIP Software License: Paul Bakker                                      | 161             |

| IwIP Software License: Paul Mackerras                                   | 161             |

| IwIP Software License: Regents of the University of California          | 161             |

| IwIP Software License: Swedish Institute of Computer Science            | 161             |

| IwIP Software License: Sun Microsystems, Inc.                           | 162             |

| IwIP Software License: The NetBSD Foundation, Inc.                      | 162             |

| IwIP Software License: Tommi Komulainen                                 | 162             |

| NetServices Software License: Carnegie Mellon University                | 162             |

| WinPCAP Software License: CACE Technologies                             | 162             |

| WinPCAP Software License: Regents of the University of California       | 162             |

| Xilinx MIT Software License: Xilinx, Inc.                               | 163             |

| Xilinx Permission Software License: Xilinx, Inc.                        | 163             |

| FreeRTOS Software License: Amazon.com, Inc. or its affilialtes          | 163             |

| FreeRTOS Software License: Amazon.com, Inc. or its affilialtes, Xilinx, | <i>Inc.</i> 163 |

Index

164

# Introduction

# **Overview**

Thank you for choosing **UDE**<sup>®</sup> **Universal Debug Engine 2025**, one of the most powerful development workbenches available for the 64-bit architectures S32V234, the 32-bit architectures AURIX<sup>™</sup>, TriCore<sup>™</sup>, S32G, S32S, Power Architecture<sup>™</sup>, Cortex<sup>™</sup>-M/R/A, ARM<sup>™</sup>-7/9/11, RH850, R-Car, SuperH<sup>™</sup> SH-2A, RISC-V, ARC and for the 16-bit architectures C166, ST10, XC166, XC2000, XE166, C166CBC, C166S V2 derivatives.

The **UDE**<sup>®</sup> **Universal Debug Engine** workbench lets you edit and organize your projects, supports you while building the applications and lets you run and test your software for example on a Starterkit board in a very convenient and cost-efficient way. The vast capability of the UDE<sup>®</sup> High-End Debugger enables you to develop fast and reliable software as well as to get short turn-around times for your microcontroller projects.

The software which you are about to install is the UDE<sup>®</sup> Standard License software. Included with the full licensed version comes a high-speed communication hardware which speeds up downloading your application into the target system. It offers a flexible way of communication via various communication channels to the supported microcontroller.

Special versions of UDE<sup>®</sup> like the **UDE<sup>®</sup> Memtool Flash/OTP Memory Programming Tool** are available on your request.

This **UDE Manual Appendix.pdf** describes the Hardware devices of **UDE**<sup>®</sup> **Universal Debug Engine**. It is an appendix of the **UDE Manual.pdf**. Please see the compatibility list in this manual below or the actual list on our Web site for supported MCUs.

**Note:** You are invited to browse to our Web site at <u>https://www.pls-mc.com/</u> to get the newest information or to download the latest version of **UDE<sup>®</sup> Universal Debug Engine**.

# Feedback

PLS welcomes feedback on our products and documentation's. If you have any comments, suggestions or improvements about the products you are using, please use the Feedback Form from our Web Site <u>https://www.pls-mc.com/</u>, send an e-mail to <u>support@pls-mc.com</u> or call our Support Line.

# **Appendix A – Safety Instructions**

# **Safety Instructions for Products and Equipment**

**Warning**! It is critical that you read and follow this safety advice, the product description including technical data and the associated technical documentation. Do not use the product if you cannot read and/or understand the Information for safe operation. If you do have questions for safe operation, please contact the PLS support at <a href="mailto:support@pls-mc.com">support@pls-mc.com</a>.

This PLS product enables users to control systems which accomplish safety functions (e.g., in electronic control systems), to change safety relevant data, or to allocate those for further processing. Hence, the application of this product can be hazardous. Improper use and unskilled application without adequate instruction and experience in handling of such products may cause threats to life and physical conditions as well as damages to property.

Our products have been developed and released exclusively for use in applications defined in the product description.

Fitness and suitability of the products for any intended use beyond the utilization for which the products have been released (e. g. other stresses/strains or technical conditions) need to be verified by the user on his own authority by taking appropriate actions and measures (e. g. by means of tests).

- PLS products made available as beta versions of firmware, hardware and software are to be used exclusively in testing and evaluation. These products may have not sufficient technical documentation and may not fulfill all requirements for quality and accuracy for market released series products. Therefore, product performance may differ from the product description and your expectations. The product should be used only in controlled test environments. Do not use data and results from beta versions without prior and separate verification and validation and do not pass them to third parties without prior examination.

- Do not use this product if you do not have proper experience and training in using the product.

- Data of any kind, which have been identified or collected by using PLS products, have to be verified with respect to reliability, quality and suitability prior to any use or dissemination.

- When using this product with systems which accomplish safety functions (e.g., in electronic control systems) that influence system behavior and can affect the safe operation of the system, you must ensure that the system can be transitioned to a safe condition (e.g. emergency shutdown or emergency operation mode) if a malfunction or hazardous incident should occur.

- All applicable regulations and statutes regarding operation must be strictly followed when using this product

- It is recommended to use the products only in closed and designated test environment.

**Warning!** If you fail to follow this safety advice, there might be a risk of death, serious injury or property damage. PLS and their representatives shall not be liable for any damage or injury caused by improper use of the product. PLS provides trainings regarding the proper and intended use of this product.

# **Regulatory Compliance and Compliance Statements**

The UADx hardware is in conformity with the protection requirements of the EU Council Directive EMC 89/336/EWG, EMC 2004/108/EC, EMC 2014/30/EC. The UADx hardware has been tested and found to comply with the limits for Class B Information Technology Equipment according to the European Standard EN 55022, EN 55024.

The UADx hardware complies with the relevant provisions of the RoHS Directive for the European Union.

#### Software

- Install the software only on systems which fulfill the minimum requirements both in hard- and software.

- For installation of the software administrator rights are required to copy files in directories which are protected by the Windows OS, to install device drivers and modify the registry.

- The software enables the in-depth control of embedded systems. It should only be operated by persons who have the necessary expertise in the systems.

- Incorrect usage of the software can lead to irreparable destruction of components in the connected systems. This concerns in particular components whose integrated permanent memory (e.g. FLASH, PCM) is protected by special mechanisms.

- There is a particular danger if mechanical devices such as motors or actuators are controlled by the embedded systems. In this case, all necessary precautions must be taken to avoid accidents, e.g., emergency shutdown.

- There is also a particular danger if the embedded systems switch voltages that exceed the permissible contact voltages. In this case, all precautions must be taken to avoid accidents, e.g. insulation.

# **Electrical Safety Instructions**

The UDE<sup>®</sup> Universal Debug Engine shall only be used according to the installing instruction of the **UDE Manual.pdf** and **UDE Manual Appendix.pdf**. Any external power supply used with the Universal Access Device (UAD2<sup>pro</sup>, UAD2<sup>+</sup>, UAD2<sup>next</sup>, UAD3<sup>+</sup> ...) and its components shall comply with the relevant regulations and standards applicable in the country of intended use.

Please observe the following safety instructions when using the power supply:

- Always use the supplied power adapter, and connect it to an AC outlet of the rated voltage and frequency. If an AC adapter other than those specified by PLS is used, it may result in damage to the UADx and its accessories or AC adapter, fire or electric shock.

- Do not insert or disconnect the AC plug with wet hands. Doing so may cause electric shock.

- Insert the power plug fully and securely. Incomplete insertion may cause fire or electric shock.

- The power supply unit should be connected to an easily accessible socket outlet in the immediate vicinity of the unit.

- Always disconnect the power cord by holding the power plug. Pulling the power cord itself may damage it and cause fire or electric shock.

- Ensure that the device connections do not come into contact with liquids and do not touch them with wet or greasy hands or metal objects. If liquid gets into the device, stop using the device immediately and contact <u>support@pls-mc.com</u>.

- Do not store the devices in environments with high humidity or where the temperature may change suddenly. If condensation has formed, switch the devices off immediately and wait until all water drops have evaporated.

- Do not pour liquid substances over the UADx and its accessories or drop other objects on it, this could cause serious damage to the UADx and its components. If this should happen please stop all work with the UADx and its accessories immediately and contact <u>support@pls-mc.com</u>.

- Do not disassemble or attempt to repair the equipment. If a device is damaged, stop using the device immediately and contact <u>support@pls-mc.com</u>. Do not touch damaged areas. Avoid contact with eventually spilled liquids.

- If the UADx and its accessories is visibly damaged or its functionality is limited, it must not be used without prior instruction from support staff (<u>support@pls-mc.com</u>). Especially if components are damaged where voltage is flowing through them. These must be replaced by the manufacturer in order to avoid hazards.

- Unplug the power cord from the wall outlet during a thunderstorm or prolonged absence! Otherwise, damage to the unit could be caused by overvoltage.

#### **Mechanical Safety Instructions**

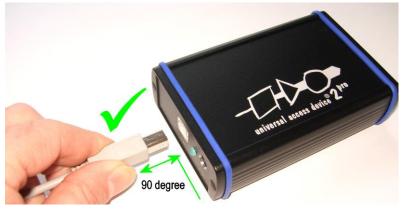

- Hold the head of the USB cable with your index finger and thumb on both sides and insert the cable straight into the USB port as shown in the illustration below. Make sure that you insert it straight and not at an angle.

- Hold both sides of the USB cable with your index finger and thumb at the point where it is connected to the computer and carefully **pull it out** horizontally to remove the cable from the USB port.

> Do not insert or remove a USB plug with excessive force.

- Do not plug in or pull out the USB plug upwards, downwards, left, right or forwards.

- > Do not pull or tug on the USB cable when plugged into the port.

# **Safety Instructions**

- Do not use the Universal Access Device (UAD2<sup>pro</sup>, UAD2<sup>+</sup>, UAD2<sup>next</sup>, UAD3<sup>+</sup> ...) and its accessories in places where flammable or combustible gases (gasoline etc.) are present. Doing so may cause a fire.

- The UADx and its components should be operated in a well-ventilated environment and should not be covered. The UADx and its accessories are only intended for use inside buildings.

- > The UADx and its components should be placed on a stable, flat surface in use.

- Do not use excessive force when using the equipment. Do not pull on cables or bend them too much.

- > Do not expose the devices to fire, microwaves or high temperatures.

- The UADx and its accessories must not be operated if it is damaged, or if smoke or odd smells occur. Doing so may result in a fire. In such situations, disconnect the power adapter from the AC outlet, and contact <u>support@pls-mc.com</u>.

- Make sure that the UADx and its accessories is stored at ground level and in a position that does not endanger persons and surrounding equipment.

- Do not place the UADx and its accessories on an unstable or sloping surface. Doing so may result in its dropping or overturning, causing injury. Be careful not to drop the UADx and its accessories when carrying it.

- Before cleaning, remove all connected cables to avoid the risk of electric shock. Clean the outside of the devices only, using a soft, damp cloth. Do not use chemicals or abrasives. Avoid under all circumstances the penetration of moisture into the device.

- The use of spare parts, accessories and special equipment which have not been tested and approved by PLS can have a negative influence on the function and properties of the UADx and its components. Therefore, PLS is not liable for any resulting damage.

- Improper operation of the UADx and its accessories may cause damage to the devices or other property. It may therefore only be used in technically perfect condition and for its intended purpose in accordance with the operating instructions given in the manual.

- Safe use of UADx and its accessories is only possible if the user manual is read completely and the instructions are followed completely. Non-observance of the instructions can lead to considerable damage or accidents.

- Anyone using UADx and its accessories must have access to the user manual. The user manual can be found here: in the delivery content of the UDE<sup>®</sup> as printed manual, UDE<sup>®</sup> Software installation as PDF.

- > Keep these operating instructions in a safe place for later use.

- The product may only be used by persons instructed in the safe use of the product and understand the resulting dangers.

- Children should be supervised to ensure that they do not play with the UADx and its components.

- Keep the devices, all accessories and packaging materials out of reach of children and pets. Small objects such as the packaging materials could be accidentally swallowed. Cables could be tied around the neck.

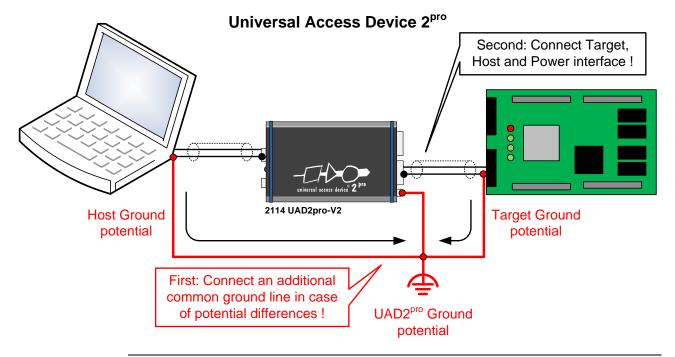

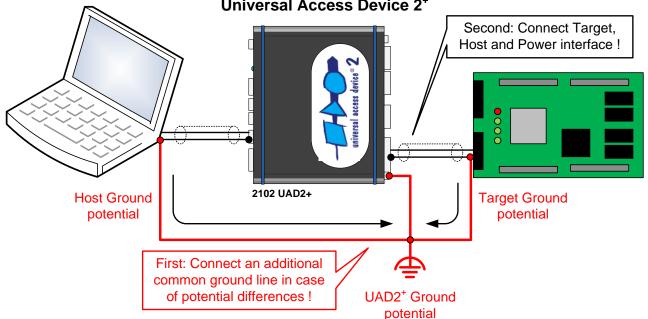

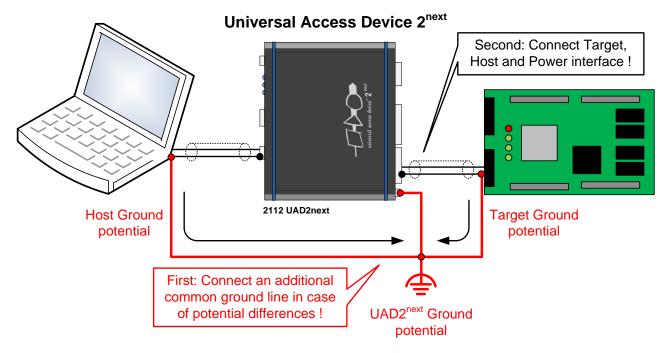

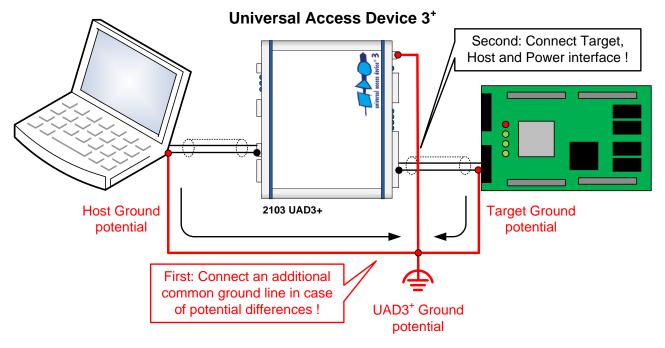

# **Static Electricity Precautions**

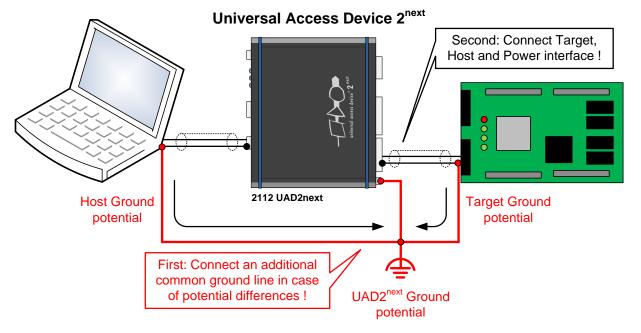

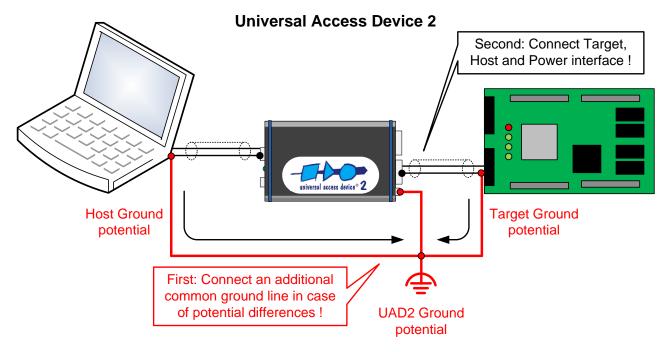

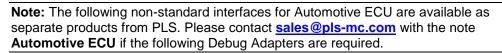

Because of the **non-hot-pluggable** 1.65 Volts / 5.0 Volts properties of the **JTAG/DAP/SWD** connectors, these ports are endangered especially by electrostatic discharging. The maximum voltage on these pins must not exceeded 5.5 Volts against the UAD's ground, especially in the case that the ground planes are not connected first. To protect your hardware against damage from static electricity and ground potential discharge, you have to follow some basic precautions:

- 1. Before you change any cable connections from the Access Device, please **remove the power** from the Access Device and your target system.

- 2. Ensure that the **static electricity** and **ground potentials** between the Access Device, the host PC and the target hardware are **balanced**. If there is a danger of high potential differences, you must connect the Access Device, the host PC and the target hardware to the same ground domain **via a low resistance connection**.

3. Establish the target connection and **power on** the systems.

**Attention!** All Universal Access Devices are equipped with a **ground socket** on the front side. Please use this ground socket for discharging the static electricity and balancing ground potentials between the Universal Access Device, the host PC and the target hardware **BEFORE** you connect the target hardware to the Access Device.

# Firmware updates

time!

**Attention!** When a new version of UDE<sup>®</sup> is started the first time, a firmware update may be executed on the Universal Access Device (UAD2, UAD2<sup>pro</sup>, UAD2<sup>next</sup>, UAD3<sup>+</sup>). This may take some more time than usual for the 'target connect' operation. Please **DO NOT** power off or unplug the access device while this

# **Original Components of Delivery**

A proper function of the UDE<sup>®</sup> Universal Debug Engine and its hardware devices is only guaranteed for working with the original components tested and delivered by PLS.

These parts can be identified by an inhered UDE® label:

The delivered components are verified by the recommends and standards of the chip manufactures. Please see the chapter **Delivery Contents** of the **UDE Manual.pdf** for further hints.

# Appendix A.1 – Hardware Description UAD2 \*)

# Description

Universal Access Device 2 as an add-on for the UDE<sup>®</sup> Development Environment for microcontrollers offers a flexible and fast solution for testing software applications on customer-specific target systems.

- Universal Access Device 2 offers high communication speed in conjunction with PCbased high-speed communication hardware that makes short turn-around cycles in software development possible.

- Universal Access Device 2 supports C16x / ST10, TriCore, XC166, XC2000, XE166, ARM7, ARM9, ARM11, Cortex-M3, Power Architecture, SuperH SH-2A and XScale derivatives with On-Chip Debug Support (OCDS)

- > Supported communication channels are JTAG, DAP, SWD, ASC, SSC, CAN.

Universal Access Device 2 is a good solution for supporting target system communication channels beside ASC that are by default not available in the target system.

Accessing the target system is supported via DAP, JTAG, SWD, SSC, CAN as well as ASC and CAN bootstrap loader interfaces, maximum flexibility together with fast communication and minimum system resource consumption is achieved.

**Note:** A proper function of the UDE<sup>®</sup> Universal Debug Engine and its hardware devices is only guaranteed for working with the original components tested and delivered by PLS. The delivered components are verified with the recommends and standards of the chip manufactures.

\*) Please note the UAD2<sup>pro</sup> replaces the UAD2. For new projects, the UAD2 is no longer available. Of course, all existing UDE/UAD2 licenses will be maintained continuously for the next years without limitations.

# **Product Features**

Universal Debug Interface for the UDE® Integrated Development Environment.

- DAP Interface via additional Debug Adapter (variable speed between 2 and 50 MHz) for debugging (supports TriCore AUDO Future and XC2000/XE166 with JTAG/OCDS)

- SWD Interface via additional Debug Adapter (variable speed between 2 and 25 MHz) for debugging (supports CoreSight and Cortex)

- Complete JTAG Interface via additional Debug Adapter (variable TCLK speed between 2 and 50 MHz) for JTAG/OCDS and JTAG/ARM debugging (supports all TriCore, C166CBC, XC166, XC2000, XE166, C166S V2, ARM7, ARM9, ARM11, Power Architecture OnCE and COP, SuperH SH-2A and XScale derivatives with JTAG/OCDS, JTAG/ARM, OnCE or COP module on-chip)

- > ASC (RS232), SSC (RS485), CAN Interface

- > USB 2.0 480 Mbps Host Interface available.

# **Precautions of Firmware updates**

**Attention!** When a new version of UDE<sup>®</sup> is started the first time, a **firmware update** may be executed on the Universal Access Device (UAD2, UAD2<sup>pro</sup>, UAD2<sup>next</sup>, UAD3<sup>+</sup>). This may take some more time than usual for the 'target connect' operation. Please **DO NOT** power off or unplug the access device while this time!

# **Power Supply**

For UAD2, the power is supplied by a main power supply unit (part of the delivery contents).

Attention! Do not use other main power supply units as they may damage Universal Access Device 2. Any damages or hazards arising from the use of unsuitable power supplies, over-voltage or wrong polarity are in the sole responsibility of the user and do not fall under warranty repair.

| Universal Access<br>Device 2<br>Power Supply<br>connector<br>18V DC | ge: Power Plug<br>$\emptyset = 2m \underbrace{m}_{t} + \underbrace{0}_{t} = 5.5mm$ |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------|

|---------------------------------------------------------------------|------------------------------------------------------------------------------------|

# **Driver Installation USB**

Because of the Plug 'n Play-Capabilities of the UAD2, the USB driver installation is started automatically, when the UAD2 is connected to the host PC the first time.

Please follow the driver installation guide described in UDE Manual.pdf.

# **Interface and Connector Description**

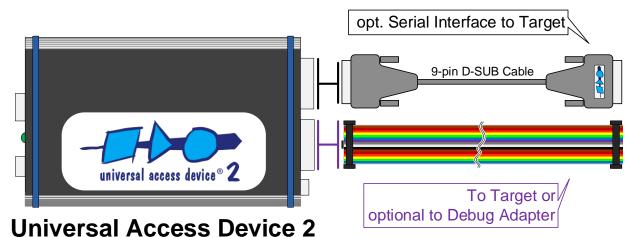

#### **Overview**

The Universal Access Device 2 features a number of interface connectors for the whole range of supported target interfaces. Via SUB-D9 connectors, serial connection between Universal Access Device 2 and the target as well as between Universal Access Device 2 and the external ASC / SSC / CAN hardware controlled by the target application is achieved. The JTAG / DAP / SWD interface is provided by a 10-pin, 16-pin or 20-pin header located on **an additional Debug Adapter**.

# **Universal Access Device 2**

| Label                     | Description                                         | Connector                                                                 |

|---------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|

| Ţ                         | Ground potential of Universal<br>Access Device 2    | 4 mm Round Connector                                                      |

| JTAG Target               | JTAG / DAP Interface to the Target                  | 16-pin Shroud Male<br>Header (or via DAP / SWD<br>/ OnCE / COP / Adapter) |

| ASC / SSC / CAN<br>Target | Combined ASC0, SSC, CAN0<br>Interface to the Target | SUB-D9 (Male)                                                             |

| Power                     | External Power Supply                               | Power Connector                                                           |

| Host/USB                  | Host Communication via USB 2.0                      | USB connector                                                             |

|                           |                                                     |                                                                           |

**Attention!** The voltage on any pin of the ASC/SSC/CAN interface must be between +12 Volts and -12 Volts and must not exceed the absolute value of 12 Volts.

# **Access Device Status Indication**

The LED on the backside of the UAD2 indicates the device state and traffic on a specific host communication interface.

| Comm (unication)                          | LED blink codes description                                                      |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------|--|--|

| LED off                                   | UAD2 not powered on (when powered on, the UAD2 or its power supply is defective) |  |  |

| LED blinking sporadically or continuously | UAD2 powered on, connection between UAD2 and Host interface established          |  |  |

## **Interface Details**

#### USB 2.0 Host Interface

Universal Access Device 2 realizes the Host Communication via the USB 1.1 or USB 2.0 interface. If the PC is not equipped with an USB interface onboard, an USB host adapter must be installed. The USB port is labelled with Host/USB.

#### **Connection Schema to the Target**

#### Asynchronous RS232-compatible Application Target Interface

The UAD2 provides a buffered asynchronous communication path between to the ASC0 of the target system controller.

| AS                                     | SC ASC Communication Interface between UAD2 and the Target System |                    |       | up to<br>1 Mbps |              |

|----------------------------------------|-------------------------------------------------------------------|--------------------|-------|-----------------|--------------|

| Connector Serial Target (Male) D-SUB9: |                                                                   |                    |       |                 |              |

|                                        |                                                                   |                    |       |                 |              |

| Pin 1                                  |                                                                   | Reserved           | Pin 2 | TxD (Targe      | et Transmit) |

| Pin 3                                  | Rx                                                                | D (Target Receive) | Pin 4 | Rese            | erved        |

| Pin 5                                  |                                                                   | GND                | Pin 6 | Rese            | erved        |

| Pin 7                                  |                                                                   | Reserved           | Pin 8 | Rese            | erved        |

| Pin 9                                  |                                                                   | Reserved           |       |                 |              |

**Attention!** The voltage on any pin of the ASC/SSC/CAN interface must be between +12 Volts and -12 Volts and must not exceed the absolute value of 12 Volts.

For connecting the target system with Universal Access Device 2, a standard 1-to-1 wired SUB-D9 cable is suitable.

#### Asynchronous RS485-compatible Target Interface (DIN 19245)

Transmission rates of up to 625 kBaud can be achieved with UAD2 via this serial interface. The definition of transmission protocol and pin assignment follows the German standard DIN 19245 for industrial networks called Profibus.

| AS      | C                                      | RS485-compatible asynchronous Communication<br>Interface |       |      | up to<br>1 Mbps |  |

|---------|----------------------------------------|----------------------------------------------------------|-------|------|-----------------|--|

| Connect | Connector Serial Target (Male) D-SUB9: |                                                          |       |      |                 |  |

|         |                                        |                                                          |       |      |                 |  |

| Pin 1   |                                        | Reserved                                                 | Pin 2 | Rese | erved           |  |

| Pin 3   |                                        | Data                                                     | Pin 4 | Rese | erved           |  |

| Pin 5   |                                        | GND                                                      | Pin 6 | Rese | erved           |  |

| Pin 7   |                                        | Reserved                                                 | Pin 8 | /Da  | ata             |  |

| Pin 9   |                                        | Reserved                                                 |       |      |                 |  |

**Attention!** The voltage on any pin of the ASC/SSC/CAN interface must be between +12 Volts and -12 Volts and must not exceed the absolute value of 12 Volts.

#### Synchronous RS485-compatible SSC Target Interface

Transmission rates up to 1 Mbps can be achieved with UAD2 via this serial interface. The transmission protocol uses the RS485 interface to reach the maximum data transmission rate for long cable distances.

| SSC | RS485 -compatible synchronous Communication<br>Interface based on the On-Chip SSC of the C16x,<br>XC166, XC2000, XE166 and TriCore Controllers | up to<br>1 Mbps |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Connecto | r Serial Target ( <b>Male</b> ): |       |        |

|----------|----------------------------------|-------|--------|

| Pin 1    | RSTIN                            | Pin 2 | MRST   |

| Pin 3    | MTSR                             | Pin 4 | SCLK   |

| Pin 5    | GND                              | Pin 6 | /RSTIN |

| Pin 7    | /MRST                            | Pin 8 | /MTSR  |

| Pin 9    | /SCLK                            |       |        |

**Attention!** The voltage on any pin of the ASC/SSC/CAN interface must be between +12 Volts and -12 Volts. It must not exceed the absolute value of 12 Volts.

#### CAN Target Interface

The Controller Area Network (CAN) bus and its associated protocol allow very efficient communication between a numbers of CAN nodes connected to the bus.

The Universal Access Device 2 may be connected therefore of the most standard evaluation boards with a CAN bus interface for the controller family. Note that the UAD2 does not contain the bus termination network. It must be added externally.

High-speed CAN networks based on ISO-DIS 11898 have a line topology and must be terminated with a 120 Ohm resistor between CAN\_H and CAN\_L lines at the last network node.

| CA                                     | CAN CAN Communication Interface |          |       | up to<br>1 Mbps |       |  |

|----------------------------------------|---------------------------------|----------|-------|-----------------|-------|--|

| Connector Serial Target (Male) D-SUB9: |                                 |          |       |                 |       |  |

|                                        |                                 |          |       |                 |       |  |

| Pin 1                                  |                                 | Reserved | Pin 2 | CA              | N_L   |  |

| Pin 3                                  |                                 | GND      | Pin 4 | Rese            | erved |  |

| Pin 5                                  |                                 | Reserved | Pin 6 | GI              | ND    |  |

| Pin 7                                  |                                 | CAN_H    | Pin 8 | Rese            | erved |  |

| Pin 9                                  |                                 | Reserved |       |                 |       |  |

**Attention!** The voltage on any pin of the ASC/SSC/CAN interface must be between +12 Volts and -12 Volts, must not exceed the absolute value of 12 Volts.

#### DAP Target Interface

The debug interface DAP was established by Infineon for 16-bit and 32-bit-microcontrollers. For UAD2 an **additional DAP Debug Adapter** is required to support the 2wire and the 3-wire DAP modes.

- ➢ I/O voltage range: 2.4 Volts − 5.0 Volts

- Power dissipation from target voltage: 100 mW (VREF = 3.3 Volts)

- > ESD Protection per signal: 15 kVolts, Capacity per signal: max 55 pF

- ➤ Resettable over-current protection for V<sub>I0</sub>:10 A (max 0.2 s time to trip, resettable).

#### TriCore, XE166, XC2000 10-pin DAP

| D/                                                                                                                                                                                              | DAP Debugging Channel for the DAP |                  |       | up to<br>50 MHz |           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|-------|-----------------|-----------|--|

|                                                                                                                                                                                                 |                                   |                  |       |                 |           |  |

| DAP Debug Adapter with 50 mil Samtec FTSH-105 connector:                                                                                                                                        |                                   |                  |       |                 |           |  |

| Pin 1                                                                                                                                                                                           |                                   | V <sub>REF</sub> | Pin 2 | DA              | .P1       |  |

| Pin 3                                                                                                                                                                                           |                                   | GND              | Pin 4 | DA              | <b>P0</b> |  |

| Pin 5                                                                                                                                                                                           |                                   | GND              | Pin 6 | DAP2_           | USER0     |  |

| Pin 7                                                                                                                                                                                           |                                   | KEY_GND          | Pin 8 | DAPEN           | USER1     |  |

| Pin 9 GND Pin 10 RESET#                                                                                                                                                                         |                                   |                  |       |                 |           |  |

| <ul> <li>Product codes for ordering the adapter and matching cable</li> <li>2000 - DAP 2-wire/3-wire communication adapter with one 10-pin 50mil Samtec FTSH-105<br/>(DAP) connector</li> </ul> |                                   |                  |       |                 |           |  |

2003 - 10-pin HD flat ribbon FTSH/FFSD cable with two 10-pin female target headers, 10" (25cm)

**Note:** The DAP Debug Adapter must be powered from  $V_{REF}$  voltage. The maximum cable length between Universal Access Device and the target system must not exceed about 25 cm (10").

#### JTAG Target Interface

TriCore, XC166, XC2000, XE166, Power Architecture, ARM7, ARM9, ARM11, XScale, SuperH SH-2A derivatives feature an on-chip IEEE1149.1-based interface for an external debugging unit.

➢ I/O voltage range: 2.4 Volts − 5.0 Volts

**Note:** The maximum cable length between Universal Access Device and the target system must not exceed about 25 cm (10").

#### TriCore, XE166, XC2000, XC166 Adapter 16-pin JTAG/OCDS

| 11001e, X2100, X02000, X0100 Adapter 10-pin 31 A0/00003                                                                                                                                        |           |                            |                |                 |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------|----------------|-----------------|-------|--|

| JTAG/OCDS Debugging Channel for the I<br>JTAG                                                                                                                                                  |           |                            | EE1149.1-based | up to<br>50 MHz |       |  |

|                                                                                                                                                                                                |           |                            |                |                 |       |  |

| JTAG De                                                                                                                                                                                        | ebug Adap | oter for 100 mil sta       | andard JTAG/C  | OCDS:           |       |  |

|                                                                                                                                                                                                |           |                            |                |                 |       |  |

| Pin 1                                                                                                                                                                                          |           | TMS Pin 2 V <sub>REF</sub> |                | REF             |       |  |

| Pin 3                                                                                                                                                                                          |           | TDO                        | Pin 4          | GN              | ND    |  |

| Pin 5                                                                                                                                                                                          |           | Reserved                   | Pin 6          | GN              | ND    |  |

| Pin 7                                                                                                                                                                                          |           | TDI                        | Pin 8          | RES             | ET#   |  |

| Pin 9                                                                                                                                                                                          |           | TRST#                      | Pin 10         | BRK             | OUT#  |  |

| Pin 11                                                                                                                                                                                         |           | TCLK                       | Pin 12         | GN              | ۸D    |  |

| Pin 13                                                                                                                                                                                         |           | BRKIN#                     | Pin 14         | OCD             | S_E#  |  |

| Pin 15                                                                                                                                                                                         |           | Reserved                   | Pin 16         | Rese            | erved |  |

| <ul> <li>Product codes for ordering the matching cable</li> <li>2018 - 16-pin flat ribbon JTAG/IFX communication cable with an Infineon defined 16-pin 100mil connector, 10" (25cm)</li> </ul> |           |                            |                |                 |       |  |

| JTAG Debugging Char      |           | annel for the IE<br>JTAG | annel for the IEEE1149.1-based<br>JTAG |                     |               |

|--------------------------|-----------|--------------------------|----------------------------------------|---------------------|---------------|

| JTAG De                  | ebug Adap | ter for 100 mil st       | andard ARM cc                          | onnector:           | 1             |

| Pin 1                    |           | V <sub>REF</sub>         | Pin 2                                  |                     | EF            |

| Pin 3                    | TRST#     |                          | Pin 4                                  | GI                  | ND            |

| Pin 5                    |           | TDI                      | Pin 6                                  | GN                  | ND            |

| Pin 7                    |           | TMS                      | Pin 8                                  | GN                  | ND            |

| Pin 9                    |           | ТСК                      | Pin 10                                 | GN                  | ND            |

| Pin 11                   |           | n.c.                     | Pin 12                                 | GN                  | ND            |

| Pin 13                   |           | TDO                      | Pin 14                                 | GN                  | ND            |

| Pin 15                   |           | RESET#                   | Pin 16                                 | GN                  | ND            |

| Pin 17                   |           | n.c.                     | Pin 18                                 | GN                  | ND            |

| Pin 19                   |           | n.c.                     | Pin 20                                 | GI                  | ND            |

| <ul> <li>2020</li> </ul> |           |                          |                                        | with an ARM defined | 20-pin 100mil |

#### Power Architecture Adapter 14-pin JTAG/OnCE

| JTAG/OnCE Debugging Channel for the IEEE1149.1- and IEEE1149.7-based JTAG                                                                                                |           |                    | up to<br>30 MHz |       |    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|-----------------|-------|----|--|

| i                                                                                                                                                                        |           |                    |                 |       |    |  |

| JTAG De                                                                                                                                                                  | ebug Adap | oter for 100 mil s | standard JTAG C | DnCE: |    |  |

|                                                                                                                                                                          |           |                    |                 |       |    |  |

| Pin 1                                                                                                                                                                    |           | TDI                | Pin 2           | GI    | ND |  |

| Pin 3                                                                                                                                                                    |           | TDO                | Pin 4           | GN    | ND |  |

| Pin 5                                                                                                                                                                    |           | ТСК                | Pin 6           | GN    | ND |  |

| Pin 7                                                                                                                                                                    |           | n.c.               | Pin 8           | n.    | С. |  |

| Pin 9                                                                                                                                                                    |           | RESET#             | Pin 10          | TN    | IS |  |

| Pin 11                                                                                                                                                                   |           | V <sub>REF</sub>   | Pin 12          | n.    | С. |  |

| Pin 13                                                                                                                                                                   |           |                    |                 |       |    |  |

| <ul> <li>Product codes for ordering the adapter and matching cable</li> <li>2023 - JTAG/OnCE communication adapter with one OnCE defined 14-pin 100mil (JTAG)</li> </ul> |           |                    |                 |       |    |  |

connector

2018 - 16-pin flat ribbon JTAG/IFX communication cable with an Infineon defined 16-pin 100mil connector, 10" (25cm)

#### Power Architecture Adapter 16-pin JTAG/COP

| JTAG/COP Debugging Channel for the IE<br>JTAG                                                                                                                 |                                                   |             | EE1149.1-based | up to<br>30 MHz |     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------|----------------|-----------------|-----|--|--|

| JTAG De                                                                                                                                                       | JTAG Debug Adapter for 100 mil standard JTAG/COP: |             |                |                 |     |  |  |

|                                                                                                                                                               |                                                   |             |                |                 |     |  |  |

| Pin 1                                                                                                                                                         | Pin 1 TDO Pin 2 QACK#                             |             |                |                 |     |  |  |

| Pin 3                                                                                                                                                         |                                                   | TDI         | Pin 4          | TR              | ST# |  |  |

| Pin 5                                                                                                                                                         |                                                   | HALTED      | Pin 6          | VF              | EF  |  |  |

| Pin 7                                                                                                                                                         |                                                   | ТСК         | Pin 8          | n.              | С.  |  |  |

| Pin 9                                                                                                                                                         |                                                   | TMS         | Pin 10         | n.              | С.  |  |  |

| Pin 11                                                                                                                                                        |                                                   | SRST#       | Pin 12         | GN              | ND  |  |  |

| Pin 13                                                                                                                                                        | HF                                                | RST#_RESET# | Pin 14         | n.              | С.  |  |  |

| Pin 15                                                                                                                                                        |                                                   | CHKSTP      | Pin 16         | GN              | ND  |  |  |

| <ul> <li>Product codes for ordering the adapter</li> <li>2026 - JTAG/COP communication adapter with one COP defined 16-pin 100mil (JTAG) connector</li> </ul> |                                                   |             |                |                 |     |  |  |

#### SuperH SH-2A Adapter 14-pin JTAG/H-UDI

| JTAG/                                                                                                                                                         | JTAG/H-UDI Debugging Channel for the IEEE1149.1-based JTAG |       |        | up to<br>30 MHz |     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------|--------|-----------------|-----|--|

| JTAG Debug Adapter for 100 mil standard JTAG/H-UDI:                                                                                                           |                                                            |       |        |                 |     |  |

|                                                                                                                                                               |                                                            |       |        |                 |     |  |

| 2                                                                                                                                                             |                                                            |       |        |                 |     |  |

| Pin 1                                                                                                                                                         |                                                            | тск   | Pin 2  | n.              | с.  |  |

| Pin 3                                                                                                                                                         |                                                            | TRST# | Pin 4  | GN              | ND  |  |

| Pin 5                                                                                                                                                         |                                                            | TDO   | Pin 6  | GN              | ND  |  |

| Pin 7                                                                                                                                                         |                                                            | n.c.  | Pin 8  | V <sub>F</sub>  | REF |  |

| Pin 9                                                                                                                                                         |                                                            | TMS   | Pin 10 | GN              | ND  |  |

| Pin 11                                                                                                                                                        |                                                            | TDI   | Pin 12 | GN              | ND  |  |

| Pin 13 RESET# Pin 14 GND                                                                                                                                      |                                                            |       |        |                 |     |  |

| <ul> <li>Product codes for ordering the adapter and cable</li> <li>2050 - JTAG/SuperH communication adapter with one Renesas SuperH defined 14-pin</li> </ul> |                                                            |       |        |                 |     |  |

100mil (H-UDI) connector

2018 - 16-pin flat ribbon JTAG/IFX communication cable with an Infineon defined 16-pin 100mil connector, 10" (25cm)

#### SWD Target Interface

The Serial Wire Debug (SWD) interface or Serial Wire Debug Port (SW-DP) is one of the features of the debug and trace technology ARM CoreSight<sup>™</sup> and is supported via a Debug Adapter. The known JTAG Debug Port (JTAG-DP) is supported furthermore. Both debug ports, the SWD and the alternative JTAG debug port can be combined to the Serial Wire JTAG Debug Port (SWJ-DP), the CoreSight/Cortex standard port. For UAD2 an **additional SWD Debug Adapter** is required to support SWD.

- ➢ I/O voltage range: 2.4 Volts − 5.0 Volts.

- Power dissipation from target voltage: 100 mW (V<sub>REF</sub> = 3.3 Volts)

- ESD Protection per signal: 15 kVolts

- > Capacity per signal: max 55 pF, Pull Downs for TCK, SWDIO

- ➤ Resettable over-current protection for V<sub>IO</sub>: 10 A (max 0.2 s time to trip, resettable).

#### Cortex Adapter 10-/20-pin Cortex

| SV                                                                            | VD | Debug            | up to<br>25 MHz |     |     |  |

|-------------------------------------------------------------------------------|----|------------------|-----------------|-----|-----|--|

| SWD Debug Adapter for 50 mil Samtec FTSH-105/FTSH-110 high density connector: |    |                  |                 |     |     |  |

| Pin 1                                                                         |    | V <sub>REF</sub> | Pin 2           | SW  | DIO |  |

| Pin 3                                                                         |    | GND              | Pin 4           | SWD | CLK |  |

| D'. E                                                                         |    |                  | D: 0            |     |     |  |

| Pin 5   | GND     | Pin 6   | SWO    |

|---------|---------|---------|--------|

| Pin 7   | KEY_GND | Pin 8   | n.c.   |

| Pin 9   | GND     | Pin 10  | RESET# |

| Pin 11* | n.c.    | Pin 12* | n.c.   |

| Pin 13* | n.c.    | Pin 14* | n.c.   |

| Pin 15* | GND     | Pin 16* | n.c.   |

| Pin 17* | GND     | Pin 18* | n.c.   |

| Pin 19* | GND     | Pin 20* | n.c.   |

\* Please note: These pins are only provided at the 20-pin micro connector.

#### SWD Debug Adapter for 100 mil standard ARM connector:

|  | <b>1</b> |

|--|----------|

|  | <b>2</b> |

| Pin 1  | V <sub>REF</sub> | Pin 2  | n.c. |

|--------|------------------|--------|------|

| Pin 3  | n.c.             | Pin 4  | GND  |

| Pin 5  | n.c.             | Pin 6  | GND  |

| Pin 7  | SWDIO            | Pin 8  | GND  |

| Pin 9  | SWDCLK           | Pin 10 | GND  |

| Pin 11 | n.c.             | Pin 12 | GND  |

| Pin 13 | SWO              | Pin 14 | GND  |

| Pin 15 | RESET#           | Pin 16 | GND  |

| Pin 17 | n.c.             | Pin 18 | GND  |

| Pin 19 | n.c.             | Pin 20 | GND  |

Product codes for ordering the adapter and matching cables

2017 - SWD extender adapter with one CoreSight defined 10-pin 50mil Samtec FTSH-105 (CoreSight) connector, one 20-pin 50mil Samtec FTSH-110 (CoreSight) and one 20-pin 100mil (SWD) connector

2003 - 10-pin HD flat ribbon FTSH/FFSD cable with two 10-pin female target headers, 10" (25cm)

2029 - 20-pin HD flat ribbon FTSH/FFSD cable with two 20-pin female target headers, 5" (12,5cm)

2018 - 16-pin flat ribbon JTAG/IFX communication cable with an Infineon defined 16-pin 100mil connector, 10" (25cm)

Note: The SWD Debug Adapter must be powered from VREF voltage. The maximum cable length between Universal Access Device and the target system must not exceed about 25 cm (10").

#### Special Target Interface for Automotive ECU

Note: The following non-standard interfaces for Automotive ECU are available as separate products from PLS. Please contact <u>sales@pls-mc.com</u> with the note **Automotive ECU** if the following Debug Adapters are required.

#### TriCore, XE166, XC2000, XC166 Adapter 10-pin MiniJTAG

| JTAG/OCDS | Debugging Channel for the IEEE1149.1-based | up to   |

|-----------|--------------------------------------------|---------|

| JTAG/0003 | JTAG                                       | 30 Mbps |

MiniJTAG/OCDS Adapter with 50 mil Samtec FTSH-105 connector:

|   | h  | 1 |

|---|----|---|

| t | Ē, |   |

|   |    |   |

| Pin 1 | BRKIN#           | Pin 2  | TRST#   |

|-------|------------------|--------|---------|

| Pin 3 | GND              | Pin 4  | TCLK    |

| Pin 5 | TMS              | Pin 6  | BRKOUT# |

| Pin 7 | RESET#           | Pin 8  | TDI     |

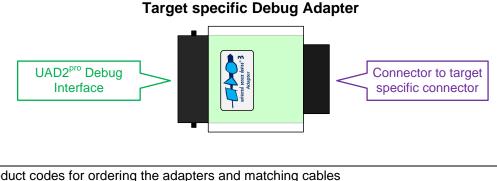

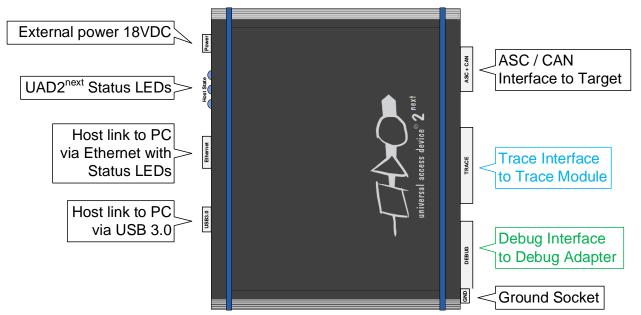

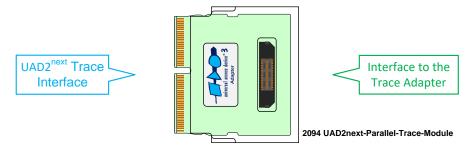

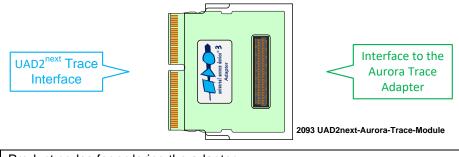

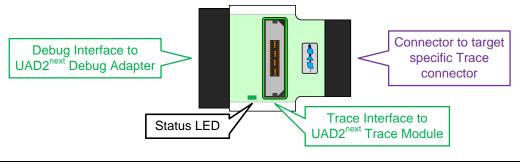

| Pin 9 | V <sub>REF</sub> | Pin 10 | TDO     |